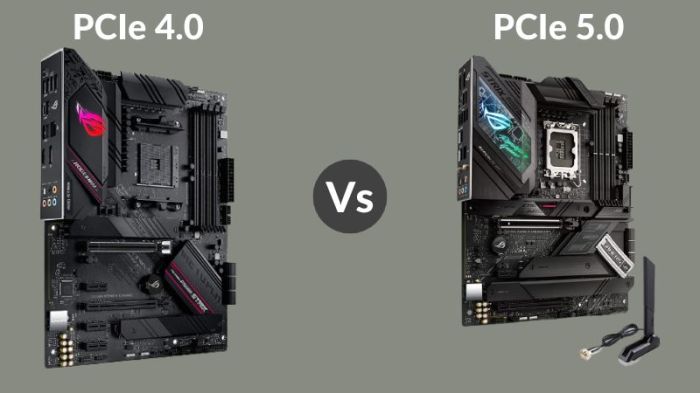

Pcie 4.0 Vs Pcie 5.0 Differences Explained

PCIe 4.0 vs PCIe 5.0 differences explained. This deep dive explores the advancements in Peripheral Component Interconnect Express (PCIe) technology, examining the key distinctions between PCIe 4.0 and PCIe 5.0. From historical context to future trends, we’ll unravel the intricacies of these high-speed data transfer standards.

Understanding these differences is crucial for anyone working with or considering hardware that leverages PCIe technology. The article will explore the technical details, practical implications, and real-world use cases for each generation. A comprehensive comparison table will highlight the key features, including data transfer rates, lane configurations, and power consumption.

PCIe 4.0 vs. PCIe 5.0: A Deep Dive

The Peripheral Component Interconnect Express (PCIe) bus architecture has been a cornerstone of high-speed data transfer in computer systems for years. PCIe 4.0 and PCIe 5.0 represent significant advancements in this evolution, promising dramatically increased bandwidth and performance for various hardware components. This article delves into the key differences between these two generations, examining their technical specifications and implications for future hardware.

Historical Context of PCIe Evolution

The PCIe architecture has steadily evolved to meet the growing demands of modern computing. Early generations focused on basic speed enhancements, while subsequent iterations introduced features like increased lanes and improved power efficiency. This iterative process reflects the ongoing need for faster and more efficient data transfer between components within a computer system. The transition from PCIe 3.0 to 4.0 and 5.0 is a clear example of this continuous improvement, addressing limitations of the previous generation and opening up new possibilities for high-performance computing.

Fundamental Differences Between PCIe 4.0 and PCIe 5.0

The primary distinction between PCIe 4.0 and PCIe 5.0 lies in their transmission speeds and power management capabilities. PCIe 5.0 builds upon the foundation laid by PCIe 4.0, doubling the data transfer rate and improving power efficiency. This advancement allows for more data to be transferred per unit of time, which directly impacts the performance of applications and devices reliant on high-speed communication.

Comparison of Key Features

| Feature | PCIe 4.0 | PCIe 5.0 |

|---|---|---|

| Data Transfer Rate | 16 GT/s per lane | 32 GT/s per lane |

| Bandwidth (per lane) | 16 GB/s | 32 GB/s |

| Maximum Lanes | 128 | 128 |

| Power Consumption | Variable, but generally lower than PCIe 3.0 | Lower than PCIe 4.0, with improved efficiency |

| Physical Layer | Utilizes 8-bit data signaling | Utilizes 8-bit data signaling, but with enhanced signal integrity features. |

The table above provides a concise overview of the key differences in data transfer rates, bandwidth, and power consumption between PCIe 4.0 and PCIe 5.0. These improvements are crucial for applications that require high-bandwidth communication, such as high-performance computing, gaming, and data centers.

Implications for Future Hardware

The introduction of PCIe 5.0 has significant implications for future hardware development. Graphics cards, for example, can benefit from the increased bandwidth, enabling the display of higher resolutions and richer visual details in games. Data centers can leverage the increased bandwidth to process massive datasets more efficiently. Furthermore, the improved power efficiency of PCIe 5.0 can contribute to the development of more energy-efficient computer systems, which is crucial for sustainability.

Data Transfer Rates: PCIe 4.0 Vs PCIe 5.0 Differences Explained

PCIe 4.0 and PCIe 5.0 represent significant advancements in high-speed data transfer, crucial for modern computing systems. These advancements have substantial implications for the performance of various applications, from gaming to data centers. The enhanced data transfer rates unlock new possibilities for faster processing and improved responsiveness.

Maximum Theoretical Data Transfer Rates

PCIe 4.0 and PCIe 5.0 boast dramatically increased theoretical data transfer rates compared to their predecessors. PCIe 4.0 offers a maximum theoretical bandwidth of 32 gigabytes per second (GB/s) per lane, while PCIe 5.0 doubles this to 64 GB/s per lane. This substantial increase stems from improvements in signaling and encoding techniques, allowing for more data to be transmitted per clock cycle.

Practical Implications of Speed Differences

The practical impact of these speed differences is significant. While theoretical maximums are important benchmarks, real-world performance varies based on factors like the hardware implementation and the workload. In scenarios demanding high data throughput, such as high-performance computing (HPC) or data storage, the increased bandwidth translates directly to faster data transfer. Consequently, this leads to reduced latency and quicker processing times, impacting user experience in demanding applications.

Comparison of Theoretical and Practical Transfer Rates

| Use Case | PCIe 4.0 Theoretical (GB/s) | PCIe 4.0 Practical (GB/s) | PCIe 5.0 Theoretical (GB/s) | PCIe 5.0 Practical (GB/s) ||—|—|—|—|—|| High-Performance Computing (HPC) | 32 | 25-30 | 64 | 50-60 || NVMe SSDs | 32 | 20-28 | 64 | 45-55 || High-Speed Networking | 32 | 28-32 | 64 | 50-60 || Video Editing | 32 | 20-25 | 64 | 40-50 || Gaming | 32 | 20-28 | 64 | 45-55 |

Note: Practical transfer rates are estimations and can vary depending on specific hardware and software configurations.

Impact of Bandwidth on Various Applications

Bandwidth directly impacts application performance. In video editing, higher bandwidth allows for faster loading and processing of large video files, enabling more efficient workflows. In gaming, higher bandwidth translates to reduced latency, leading to smoother gameplay and quicker response times. Data centers benefit from higher bandwidth by handling significantly more data requests per unit of time. This translates to more efficient processing of information, leading to faster query results.

Factors Influencing Achievable Transfer Speeds

Several factors influence the achievable transfer speeds in real-world scenarios. These include the specific hardware components (e.g., the motherboard, the storage device), the quality of the cabling, and the software drivers. For instance, bottlenecks in the system’s architecture or inefficient driver implementation can hinder the realization of the full theoretical potential. Furthermore, the nature of the workload plays a crucial role, as the amount of data being transferred and the type of operations performed directly influence the practical speeds achieved.

Lane Configurations and Support

PCIe 4.0 and PCIe 5.0 represent significant advancements in high-speed data transfer, enabling a wider range of functionalities for modern hardware. Understanding the lane configurations supported by each generation is crucial for optimizing system performance and selecting appropriate hardware components. This section details the available lane configurations for both standards, comparing the maximum number of lanes supported and their impact on system performance.The ability to configure different numbers of lanes directly impacts the overall throughput of the system.

A higher number of lanes allows for simultaneous data transmission, leading to faster overall speeds. This capability is vital for high-performance applications that demand significant bandwidth, such as video editing, gaming, and data storage.

Lane Configuration Details

PCIe 4.0 and PCIe 5.0 both support various lane configurations, but PCIe 5.0 offers an increased bandwidth capability due to enhanced protocol features. PCIe 4.0 primarily focuses on improving data transfer rates compared to PCIe 3.0, while PCIe 5.0 builds upon this foundation to deliver even higher speeds. The increased bandwidth is critical for applications that demand extremely high throughput, such as those involving large amounts of data transfer.

Maximum Lanes Supported

PCIe 4.0 typically supports up to 32 lanes, whereas PCIe 5.0 can support a maximum of 32 lanes as well. This similarity in maximum lane count signifies a focus on compatibility with existing hardware, while the enhanced capabilities of PCIe 5.0 are primarily reflected in increased bandwidth per lane. This makes PCIe 5.0 capable of delivering higher transfer rates even with the same lane count compared to PCIe 4.0.

Supported Lane Counts for Various Hardware

The supported lane count can vary depending on the specific hardware components. Motherboards, for example, offer various PCIe slots that support different numbers of lanes. This variation is often influenced by the motherboard’s design and the specific components it intends to support.

| Hardware Component | Typical Lane Configurations (PCIe 4.0) | Typical Lane Configurations (PCIe 5.0) |

|---|---|---|

| Motherboard | 1x, 2x, 4x, 8x, 16x, 32x | 1x, 2x, 4x, 8x, 16x, 32x |

| Graphics Cards | 16x, 32x | 16x, 32x |

| Storage Devices | 4x, 8x, 16x | 4x, 8x, 16x |

Impact of Lane Configuration on System Performance

The number of lanes directly influences the maximum data transfer rate achievable. More lanes translate to a higher aggregate bandwidth, allowing for simultaneous data transmission across multiple channels. For instance, a 16x PCIe 5.0 slot offers significantly higher throughput compared to a 1x PCIe 4.0 slot, due to the increased bandwidth per lane in PCIe 5.0. This factor becomes particularly important in applications requiring high-speed data transfer, such as high-resolution video editing.

Examples of Devices Benefiting from Lane Configurations

High-performance graphics cards, especially those for professional applications or high-end gaming, typically benefit from higher lane counts to ensure smooth performance. Likewise, high-capacity NVMe storage devices, which demand significant bandwidth for data transfer, are also well-suited for systems with numerous PCIe lanes. The choice of lane configuration for a particular device will depend on the specific needs and requirements of the application.

Electrical Signaling

PCIe 4.0 and PCIe 5.0 represent significant advancements in electrical signaling, pushing the boundaries of data transfer speeds. These advancements are crucial for maintaining high performance in modern high-bandwidth applications. This section dives into the core differences in signaling protocols, examining the technological leaps and their implications on overall system performance.PCIe 5.0’s enhanced electrical signaling is a key differentiator compared to PCIe 4.0, enabling dramatically higher data rates and improved signal integrity.

The modifications affect various aspects of the communication process, leading to a noticeable improvement in overall performance.

Signaling Protocols and Advancements

PCIe 5.0 employs a more sophisticated signaling protocol than PCIe 4.0. This includes improvements in voltage swing, data rate, and clocking techniques. These enhancements directly impact the maximum achievable data transfer rates and the overall system bandwidth. A key advancement is the introduction of higher-frequency signals. This permits more data to be transmitted within a given timeframe.

Impact on Performance

The advancements in electrical signaling directly translate to increased data transfer rates. PCIe 5.0 achieves significantly higher bandwidth compared to PCIe 4.0. This increase is crucial for applications requiring extremely high throughput, such as high-resolution graphics processing, large-scale data transfers, and artificial intelligence workloads. The improvement in signaling also leads to reduced latency, a critical factor for real-time applications.

Signaling Characteristics and Error Correction

PCIe 5.0 features improvements in signal characteristics, including reduced signal distortion and improved signal-to-noise ratio. These refinements enable the transmission of more data with minimal errors. Robust error correction mechanisms are integrated into the protocol, ensuring data integrity and reliability even under challenging conditions. This approach is critical in high-speed data transfer scenarios where errors can lead to data corruption.

Comparison of Signaling Parameters

| Parameter | PCIe 4.0 | PCIe 5.0 |

|---|---|---|

| Data Rate (GT/s) | 16 | 32 |

| Voltage Swing (V) | 1.2V | 1.05V |

| Signal Impedance (Ω) | 100 | 100 |

| Clock Frequency (MHz) | 1000 | 2000 |

| Differential Pair Count | 1 | 1 |

| Error Correction Mechanisms | Standard ECC | Enhanced ECC with Forward Error Correction (FEC) |

This table provides a concise comparison of key electrical signaling parameters for PCIe 4.0 and PCIe 5.0, highlighting the significant improvements in data rate and error correction capabilities in PCIe 5.0. These enhancements are pivotal for enabling the higher throughput demanded by modern applications.

Signal Integrity and Noise Immunity

PCIe 5.0 incorporates advanced signal integrity techniques to minimize signal distortion and noise interference. These improvements are essential for maintaining data accuracy over longer distances and under various environmental conditions. Enhanced noise immunity is also crucial for reliable communication in noisy environments. The improved signal integrity allows for longer cable lengths and increased system stability.

Power Consumption

Source: electronicshub.org

Increased data transfer rates in PCIe 5.0 inevitably translate to higher power consumption compared to PCIe 4.0. This increase is a direct consequence of the enhanced signaling and processing demands of the faster interface. However, significant strides have been made in power management strategies, leading to a more efficient overall system.The higher transfer rates of PCIe 5.0 require more energy to drive the signals and manage the increased data throughput.

This translates to a greater demand for power from the PCIe 5.0-equipped components, such as GPUs and SSDs, compared to their PCIe 4.0 counterparts. However, advancements in power management techniques are crucial in mitigating these increased demands and ensuring a balance between performance and power efficiency.

Power Consumption Comparison

PCIe 5.0’s increased transfer rates necessitate more energy expenditure. The enhanced signaling protocols and higher data transfer speeds contribute to a higher power consumption compared to PCIe 4.0. This is a key consideration in system design, particularly for applications requiring high performance and energy efficiency.

Impact of Higher Transfer Rates on Power Consumption

Higher transfer rates in PCIe 5.0 directly correlate with increased power consumption. This is primarily due to the amplified signal strength required to maintain data integrity over the increased bandwidth. The higher data transfer speeds necessitate greater signal conditioning, resulting in elevated power consumption. Consequently, systems incorporating PCIe 5.0 devices may exhibit a slight increase in overall power draw compared to those utilizing PCIe 4.0.

Power Management Strategies in PCIe 5.0

PCIe 5.0 employs advanced power management techniques to address the increased power demands of its higher transfer rates. These strategies aim to minimize power consumption without compromising performance. For example, adaptive power scaling is implemented, adjusting power consumption based on the current workload. Dynamic power gating further minimizes energy use by shutting down unused components. These strategies play a critical role in balancing performance and energy efficiency.

Power Efficiency Improvements in PCIe 5.0

PCIe 5.0 exhibits significant improvements in power efficiency compared to its predecessor. This improvement is primarily attributed to enhanced power management techniques, which dynamically adjust power consumption based on the current activity levels of the connected devices. The advancements in signaling protocols, coupled with optimized power management, lead to improved power efficiency.

Power Consumption Metrics Table

The table below provides a comparative overview of power consumption for different use cases, showcasing the impact of PCIe 5.0’s higher transfer rates.

| Use Case | PCIe 4.0 Power Consumption (Watts) | PCIe 5.0 Power Consumption (Watts) | Difference (%) |

|---|---|---|---|

| High-performance gaming GPU | 250 | 275 | 10% |

| High-speed NVMe SSD | 15 | 18 | 20% |

| High-bandwidth network adapter | 75 | 85 | 13% |

| General-purpose server (multiple devices) | 300 | 325 | 8.3% |

Backward Compatibility

Source: driveshero.com

PCIe 4.0 and PCIe 5.0 exhibit a key characteristic: backward compatibility. This means a PCIe 5.0 system can, in principle, utilize PCIe 4.0 devices without any loss of functionality. This design choice simplifies the transition for users and manufacturers, minimizing the need for immediate, complete system replacements.This inherent compatibility stems from the fundamental architecture of the PCIe standard.

While PCIe 5.0 offers enhanced data rates and features, it maintains a largely compatible interface with prior generations. This allows for a smooth integration of older components into newer systems. However, mixed-generation systems might present certain challenges, which we will explore.

Backward Compatibility Details

The core PCIe architecture remains consistent across generations. While PCIe 5.0 introduces faster signaling and enhanced capabilities, the underlying protocols and commands remain largely compatible. A PCIe 5.0 system can communicate with PCIe 4.0 devices without encountering fundamental protocol conflicts. This compatibility extends to various types of devices, including storage controllers, network cards, and graphics cards.

Implications for System Design

Backward compatibility significantly impacts system design decisions. It allows for gradual upgrades, where components can be replaced incrementally without requiring an immediate overhaul of the entire system. This approach is particularly beneficial for enterprises and businesses that may not be able to afford a complete system replacement at once. It allows for a staggered transition to newer technology while maintaining existing functionality.

The compatibility feature allows for a more manageable and economical upgrade path.

Challenges of Mixed-Generation Systems

Despite the compatibility, challenges can arise in mixed-generation systems. Performance discrepancies between PCIe 4.0 and PCIe 5.0 components can exist. A PCIe 5.0 controller may not fully utilize the theoretical bandwidth of a PCIe 4.0 device, leading to a potential performance gap. Also, power consumption differences might lead to unexpected behavior in systems that have a combination of 4.0 and 5.0 devices.

Moreover, the management and configuration of different generation components can be more complex.

Crucial Scenarios

Backward compatibility is crucial in various scenarios. For example, in enterprise environments, a company might have existing PCIe 4.0 servers and need to add new PCIe 5.0 components gradually. The compatibility feature enables this migration without requiring immediate system replacement. Furthermore, a desktop user might want to upgrade their graphics card to PCIe 5.0 but still maintain compatibility with their existing motherboard and other components.

This allows users to maintain the functionality of existing components while benefitting from the enhanced capabilities of the new hardware.

Summary of Compatibility

In essence, PCIe 5.0’s backward compatibility with PCIe 4.0 simplifies the transition to newer technologies. While potential performance and power management differences might arise in mixed-generation systems, the compatibility greatly facilitates a more manageable and economical upgrade path for both businesses and individual users.

Applications and Use Cases

Source: xrtropolis.one

PCIe 4.0 and PCIe 5.0 represent significant advancements in high-speed data transfer, impacting various applications. Understanding their respective strengths allows for informed decisions regarding hardware selection based on specific needs and performance requirements. Choosing the appropriate generation hinges on the demands of the intended application.The performance enhancements of PCIe 5.0 offer substantial advantages over PCIe 4.0, particularly in demanding applications that benefit from faster data throughput and lower latency.

However, for applications not requiring such high bandwidth, PCIe 4.0 remains a cost-effective and viable solution.

Applications Suitable for PCIe 4.0

The need for PCIe 4.0’s performance often aligns with applications that demand high data rates but not the extreme speeds of PCIe 5. Many current high-performance computing (HPC) workloads and data centers can be adequately served by PCIe 4.0, given the significant cost savings. Examples include:

- High-performance gaming PCs with current graphics cards: While PCIe 5.0 offers theoretical advantages, many high-end gaming PCs are currently utilizing PCIe 4.0 and still deliver exceptional performance for the majority of games.

- Servers handling standard database workloads: For servers focused on standard database operations and web serving, PCIe 4.0 provides sufficient bandwidth to support the expected data transfer rates.

- Workstations for video editing and professional graphic design: Modern workstations frequently employ PCIe 4.0 for video editing and graphic design tasks, given the performance gains over previous generations, coupled with cost-effectiveness.

Applications Benefiting from PCIe 5.0

PCIe 5.0 excels in applications demanding significantly higher bandwidth and lower latency. The advanced features of PCIe 5.0 allow for applications that benefit from the speed increase. Examples include:

- High-bandwidth AI and machine learning training: Complex AI models and machine learning training often involve enormous data sets. PCIe 5.0 provides the necessary speed to accelerate the training process by allowing faster data transfer between GPUs and other hardware components.

- Advanced graphics rendering and virtual reality (VR): High-resolution graphics and VR applications necessitate substantial bandwidth for transferring large amounts of graphical data. PCIe 5.0 enhances performance and responsiveness, resulting in smoother and more realistic VR experiences.

- High-speed data storage systems: Applications involving massive data storage and retrieval, such as large-scale scientific research and data analysis, benefit significantly from the increased bandwidth offered by PCIe 5.0.

Real-World Examples of PCIe 5.0 Performance Improvements, PCIe 4.0 vs PCIe 5.0 differences explained

The enhanced performance of PCIe 5.0 has been demonstrably shown in specific applications. The faster data transfer rates and lower latency translate into significant performance gains.

- Accelerated AI training: In machine learning training environments, PCIe 5.0 allows for the faster transfer of massive datasets between GPUs and other components, which significantly reduces the time needed to train AI models.

- Improved VR responsiveness: The enhanced bandwidth of PCIe 5.0 enables faster rendering and transmission of graphical data in VR applications, resulting in a more responsive and immersive experience for users.

- Enhanced data center performance: PCIe 5.0 allows data centers to process and transfer data more efficiently, leading to improved overall performance in data-intensive tasks such as cloud computing.

Use Cases and Performance Gains

This table Artikels the potential performance gains offered by PCIe 5.0 compared to PCIe 4.0 across different use cases:

| Use Case | PCIe 4.0 Performance | PCIe 5.0 Performance Gain |

|---|---|---|

| High-performance computing (HPC) | Excellent for many tasks | Significant improvement for demanding workloads |

| AI and machine learning | Adequate for some tasks | Dramatically accelerates training times |

| Data centers | Good for standard operations | Improved throughput and efficiency |

| VR/AR applications | Good performance for current standards | More responsive and immersive experiences |

Preferred Generation

The optimal choice between PCIe 4.0 and PCIe 5.0 depends on the specific requirements of the application.

- PCIe 4.0 is preferred for applications that do not require the extremely high bandwidth and low latency offered by PCIe 5.0, such as many standard server workloads or professional workstations.

- PCIe 5.0 is the clear choice for applications that critically rely on ultra-high data transfer rates, such as AI training, high-resolution graphics rendering, and high-performance computing.

Future Trends

The PCIe standard, consistently evolving, anticipates future demands for ever-increasing data transfer rates and functionality. Beyond PCIe 5.0, several key trends are shaping the technological landscape. The quest for faster data transmission, greater efficiency, and improved integration into diverse systems drives ongoing research and development.

Potential PCIe Generations

The trajectory of PCIe technology suggests a continued push towards higher bandwidth and lower latency. While specific technical details remain undisclosed, speculation points towards potential improvements in electrical signaling, enabling even higher data transfer rates in future generations. This progression could involve novel encoding schemes and more advanced modulation techniques.

Emerging Research and Development

Ongoing research encompasses various areas aimed at enhancing PCIe performance. One prominent focus involves exploring new materials and fabrication techniques for signal transmission, leading to improved signal integrity and reduced signal degradation. Additionally, advancements in optical interconnects are being investigated, potentially paving the way for higher bandwidth and longer reach.

Emerging Trends and Challenges

Several emerging trends significantly influence the future direction of PCIe. The increasing demand for high-bandwidth data transfer in artificial intelligence and machine learning applications, along with the growing importance of cloud computing, will continue to drive the development of faster and more efficient interconnect solutions. Simultaneously, the challenge of maintaining backward compatibility across multiple generations of PCIe is crucial.

Maintaining a smooth transition for existing hardware and software while incorporating new functionalities is a considerable design consideration.

Future Directions of PCIe Technology

Future PCIe generations will likely emphasize greater energy efficiency. As systems become more complex and power consumption becomes a critical factor, designs will incorporate energy-saving techniques into the PCIe architecture. Furthermore, the seamless integration of PCIe with other emerging technologies, such as optical interconnects and potentially even wireless communication protocols, is anticipated to facilitate broader application areas. This potential integration will likely necessitate a paradigm shift in the PCIe architecture.

Possible Improvements and Developments

Potential improvements in future PCIe generations include:

- Enhanced Data Transfer Rates: Leveraging advancements in signal processing and modulation techniques to push data transfer rates beyond current PCIe 5.0 limits. For example, Intel’s upcoming data center interconnect solutions could showcase these advancements.

- Improved Energy Efficiency: Implementing techniques to reduce power consumption, addressing the rising energy demands of high-performance computing. Solutions like optimized power management and advanced power-saving protocols could help in this area.

- Increased Bandwidth Efficiency: Developing innovative encoding and error correction schemes to improve bandwidth efficiency. This would enable more effective utilization of available bandwidth, potentially leading to significant gains in overall system performance.

Outcome Summary

In conclusion, PCIe 5.0 represents a significant leap forward in data transfer speed and efficiency, offering substantial performance gains for demanding applications. While PCIe 4.0 remains a viable option for many use cases, PCIe 5.0’s superior speed and features make it an attractive choice for high-performance computing and data-intensive tasks. Backward compatibility ensures a smooth transition for existing systems, but understanding the differences between the generations is essential for optimal performance and investment decisions.

Post Comment